技術情報TECHNOLOGY

Chapter 1システム概要

メモリテストシステムとは、メモリデバイスに信号及び電源を与え、出力信号を期待値と比較し、良否判定を行う検査装置です。

メモリの製造プロセスはウエハ製造、ウエハ検査を行う「前工程」と組立(パッケージ)、パッケージ検査を行う「後工程」に大分されますが、弊社では主に前工程の検査装置を開発しています。

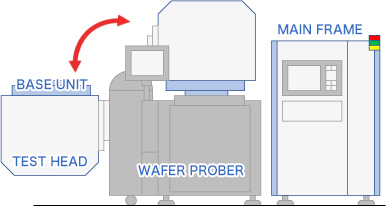

テストシステムは、メインフレームとテストヘッドで構成され、テストヘッドはウエハを搬送するプローバとドッキングします。

ベースユニットには探針をもつプローブカードが装着され、ウエハの電極に接触して測定が行われます。

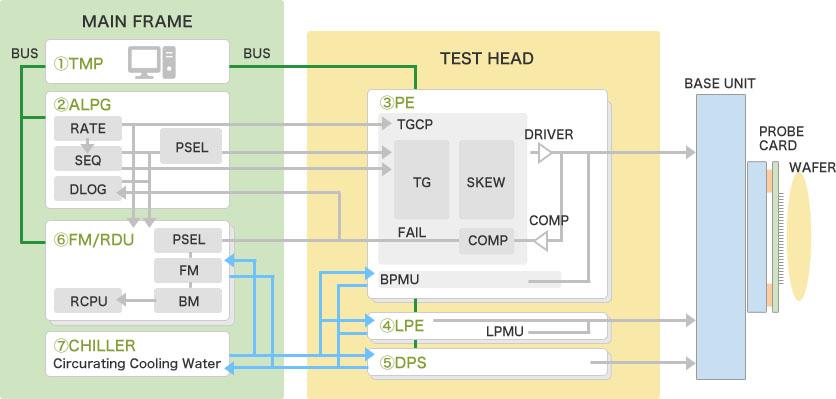

テストシステムの内部は、下図の機能を持ったブロックが多チャンネルで構成され、メモリデバイスを一度に多数個測定することができます。

| ① TMP(Test Management Processor) | プログラム作成、ハードウエア制御、テスト結果処理等、テストシステムの管理を行う。 |

|---|---|

| ② ALPG(Algorithmic Pattern Generator) | アドレス、データパターン、その他制御パターンを発生させる。 |

| ③ PE(Pin Electronics) | デバイス各ピンへのパターン信号の印加とDC測定、デバイスの出力データのPass/Fail判定を行う。 |

| ④ LPE(Level Pin Electronics ) | デバイスへの高電圧/高電流の印加、その電流/電圧の測定を行う。 |

| ⑤ DPS(Device Power Supply) | デバイスへの電源供給、その電源電流測定を行う。 |

| ⑥ FM/RDU(Fail Memory / Redundancy Unit) | デバイステストのFail発生状況を格納するとともに、RDUにてリペアアナリシスをバックグラウンドで実行できる。 |

| ⑦ CHILLER | 各カードに対して、冷却媒体を循環させ冷却を行う。 |

- 主な技術

- ・大規模な高速ロジック回路の集積化

・高精度なタイミング発生

・多チャンネルアナログ信号の高速伝送

・プリント基板に搭載された部品の冷却

・可動部を含む精密機構

Chapter 2統合開発環境

テストシステムは、各ユニット内のハードウェア制御プロセッサ、リペアアナリシス用リダンダンシープロセッサ、これらの統合とユーザーインターフェースを担うTMP(Tester Management Processor)を搭載し、それぞれのソフトウェアが分散・並行処理を行うことによって、テストシステムハードウェアの能力を最大限発揮させ、効率よいデバイス試験を実現します。

- プログラミング

- 多様なメモリデバイスの試験に対応するため、テストシステムハードウェアに最適化された、エンドユーザ向けのプログラム言語を提供します。 ・ テストパラメータやテストフローを記述するテスト言語 ・ メモリセルに読み書きするアルゴリズムを記述するパターン言語 ・ メモリの不良セルを検出し、どのスペアラインに置換するかを分析するリペアアナリシス言語 ・ 生産ラインでの他社装置や管理サーバーとの連携、効率的な運用をサポートするインターフェース言語

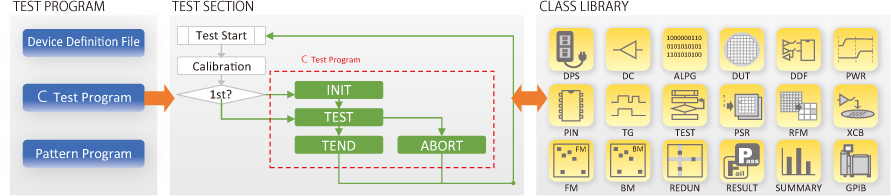

テストプログラムは、デバイスの固有情報を定義するデバイス定義ファイル、テスト言語でプログラミングされるCテストプログラム、パターン言語でプログラムされるパターンプログラムで構成されます。

Cテストプログラムは、テスティングの状態遷移に応じた4つのセクションを持ち、テストシステムのハードウエアユニットにアクセスするクラスライブラリにより作成されます。

- オペレーション

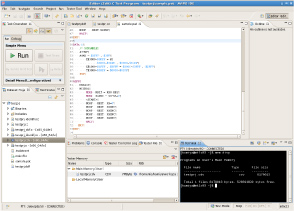

- ユーザによるプログラミングからデバッグ、デバイス評価までを、効率よくサポートする統合環境を提供します。

- Eclipseに統合された開発環境

- ・ 専用エディタのコードアシスト機能でリファレンス・マニュアルが不要 ・ タブ・インデントをスペースに変換するなど、フォーマットを一括変更 ・ コンパイルは専用ビューで管理、エラー箇所へジャンプも可能 ・ テストプログラムのデバッグはボタン一つで、ライン・ブレイクも使える

- デバイスを評価するための主な機能

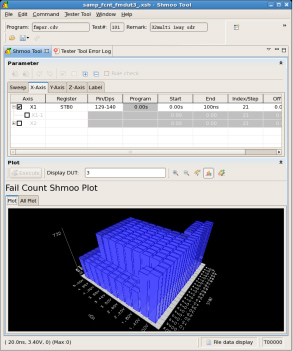

- ・ パラメータをスイープさせながら測定するシュムープロット ・ テストパラメータの一覧表示 ・ デバイスへの入出力波形の描画 ・ デバイスの不良セルの位置の描画するフェイルビットマップ ・ ボトルネックを発見するパフォーマンス解析ツール

Chapter 3リペアアナリシス

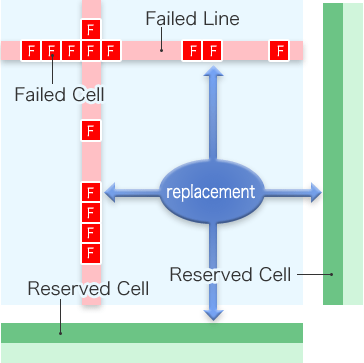

微細な前工程プロセスではプロセスが成熟しても、チップ内の全メモリセルが良品となることは難しく、多くのチップで不良セルが発生します。

不良が少数の場合、不良セルが存在するラインを予備のセル(スペアセル)で置換えて、不良品を救済する処理を行います。

この不良ラインをスペアセルと置き換えるための解析、処理を実現するための機能がリペアアナリシス(RA)です。

- RA機能の特徴

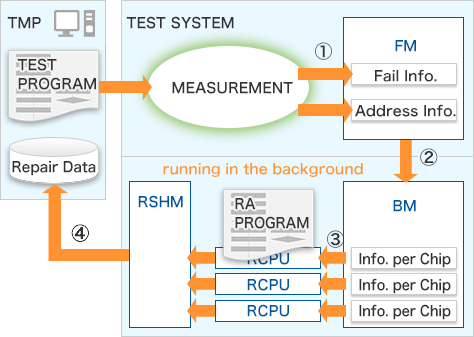

- テストシステムには、測定によって不良と判定されたメモリセルの情報を保存するフェイルメモリ(以下FM)があります。

このFMの情報を使用してRAを実行しますが、測定中でもバックグラウンド処理できるよう専用のハードウエアが用意されています。 - ・FMの情報を高速でコピーできるバッファメモリ(BM)

・RAを高速に行うための複数の専用CPU(RCPU)

・RAプログラムとテストプログラム間で高速にデータを共有できる共有メモリ(RSHM)

- RAプログラム

- 不良セルの位置をサーチし、置き換えるスペアセルを特定する解析処理は、RAプログラムで実行します。

RAプログラムは複数のRCPU上で並列に実行され、大量のデータを高速に処理することができます。 - ➀ テストプログラムによる測定でフェイル情報がFMに書き込まれる ② FMの情報がBMへコピーされた後、RAプログラムがBMの操作を開始する ③ RAプログラムは、BMよりフェイル情報を取得し、不良セルの解析・不良ラインの置き換えを行う ④ 置き換えデータをRSHMに集積し、最終的にリペアデータを作成する

- RAライブラリ

- RCPUには専用の言語システムが用意されており、ユーザが独自のアルゴリズムでRAプログラムを作成することができます。 この言語システムにはBMに対する様々なライブラリが用意されており、より効率的な解析を可能としています。

- ・IO毎のフェイルの全カウント ・対象範囲と対象IOの指定 ・指定範囲内における指定IOのフェイルのカウント/サーチ/クリヤ ・指定範囲内で指定IOのフェイルのサーチ中の1ラインカウント/サーチ/クリヤ

Chapter 4ALPG

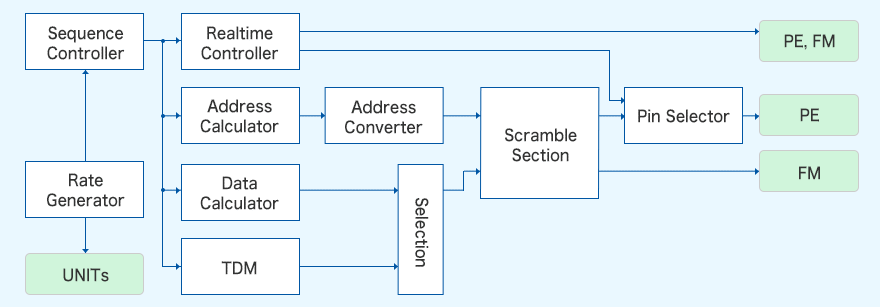

ALPGは、デバイス印加アドレスとデバイス印加パターンまたはデバイスからの期待値をPEに出力します。

同時に、バースト情報を伴ったデバイスのアドレスをFMにも出力します。これらのデータは、テストプログラムに記述されたアルゴリズムに従って発生します。

また、デバイスとテストパターンを同期させるための基準タイミング(レート)も発生します。

| シーケンス制御(Sequence Controller) | テストパターンの記述に従って、テストのスタート~エンドを制御する。 |

|---|---|

| リアルタイムコントロール(Realtime Controller) | テストパターンにおけるリアルタイムなタイミングの切り換えや、ピンセレクタの切り換え、およびストローブ、I/O 切り換えパターンの発生を制御する。 |

| アドレス演算(Address Calculator) | テストパターンのアドレス演算命令に従って、デバイスのアドレスとなるX,Yアドレスを出力する。 |

| アドレス変換(Address Converter) | アドレス演算から発生された連続的なアドレスをスペアセルのアドレスに変換する。 |

| データ演算(Data Calculator) | テストパターンのデータ演算命令に従い、デバイスのデータとなるT Dataを出力する。 |

| スクランブルセクション(Scramble Section) | ・アドレススクランブルは、アドレス演算で発生する論理アドレスを、デバイス内部の物理アドレスに変換する。 ・データスクランブルは、データ演算で発生するデータを実際のデバイスに有効なデータに変換する。 |

| ピンセレクタ(PIN Selector) | ALPGで発生したパターンデータを、デバイスのどのピンへ与えるかを選択する。 |

| TDM(T Data Memory) | データ演算では発生が困難なランダムパターンを発生する。 |

| レート発生(Rate Generator) | 基準タイミングとなるレートを発生する。 |